Hi Matt,

I have spend a few nights mapping out the RESET circuit for the MCU. On the NSX ECU, the RESET line is tied to ground so when the ECU is powered on, the MCU goes into RESET and stays in RESET. There is a transistor (Q400) that ties to the RESET line which is controlled by the backup processor (IC501 pin 17) AND something else (possibly IC402, first I/O controller but without datasheet; I am not sure if it's an input line or output line on the I/O controller) that I haven't fully mapped out. When the condition is right (perhaps after backup processor or some other circuit initializes) after power on, the RESET line is pulled high to bring the MCU out of RESET and the MCU runs the RESET vector routine.

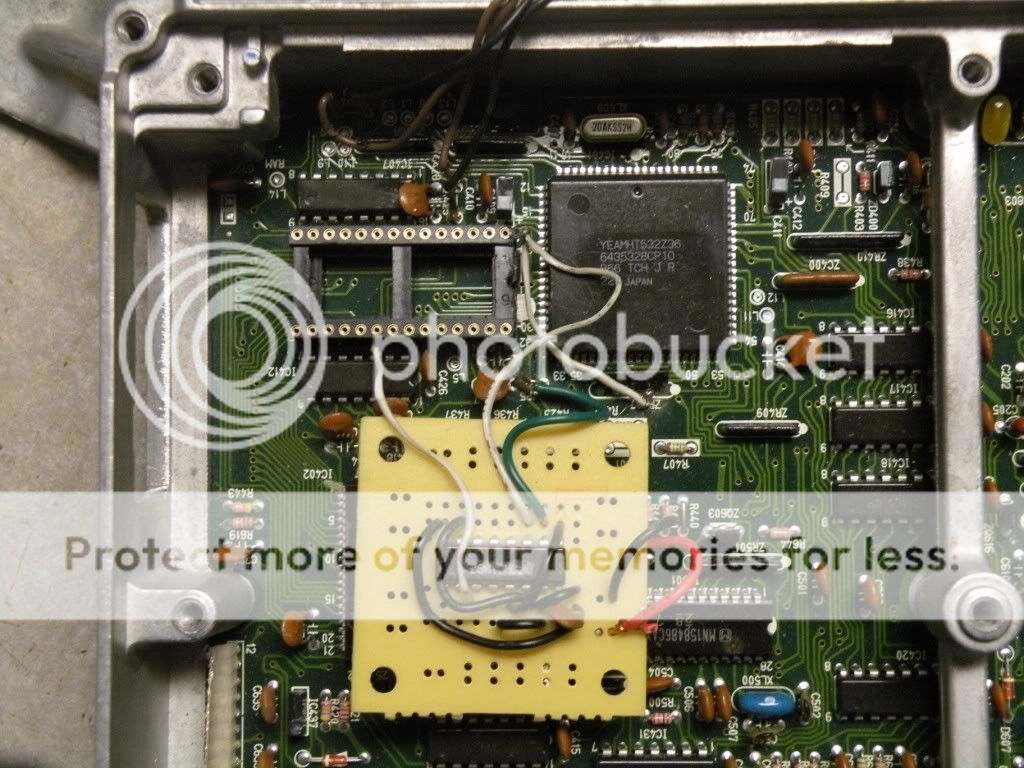

I did an experiment by removing the external ROM on purpose to make the MCU go into fault and noticed the reset loop you described. The RESET line would go low every second or so to reset the MCU (remember, RESET is active low). However, the line that triggers this reset loop is not from the backup processor (IC501 pin 17) but instead from the 2nd input which I haven't mapped out. These 2 inputs are NANDed through IC430 (quad NAND gate) on pin 12-13 with output to the RESET transistor (Q400) on pin 11. I need a few more nights to map the source of this input.

An interesting tidbit I found is that IC430 (quad NAND gates) is used for several different purposes. The first 2 NAND gates are tied in such a way to form a SR latch (flip-flop); I don't know the exact purpose of it yet but it's partially controlled by the backup process IC501 and feeds back to IC501 again. SR latch acts like a light switch; it will keep the value (set or reset) that you set it with, in effect storing a 0 or a 1. The 3rd NAND gate is used to decode MCU's A14 and A15 lines to chip enable (CE) the external ROM; active when address matches A15-A14 match 10. The 4th NAND gate is for controlling the RESET circuit I described above. It looks like Panasonic (Matsushita) changed the design a bit since the Legend ECU and used a 3-8 decoder (vs 2-4 decoder) for selecting the dual I/O controllers and a NAND gate with an inverter to select the external ROM.

I think you are right on the spot about the bus conflict. On the NSX ECU, the address decoders maps a range of addresses exclusively to each device on the bus (ROM, I/O controllers) so there is no conflict with each other. On the Legend ECU from your diagram, it's done the same way. I don't believe the data bus size would have any effect since there are several subroutine on the external ROM that the MCU calls regularly; not to mention it accesses the maps there all the time. Nissan probably used 2 32KB ROM instead of 1 64KB ROM due to cost at the time.

Since you are a 2-4 decoder, double check the decoding is mapping only to 0x0000-0xBFFF (and not something like 0x0000-0xFFFF; that could be the source of your conflict). The decoder should only be active (enables the ROM's ~CE) on the ROM when A15-A13 are these values (000-101) and doesn't include values such as 110 and 111. Maybe you can give my mod a try?

http://www.acuralegendwiki.org/images/f/f9/LegendECUExternalROM.pdf

http://www.acuralegendwiki.org/images/f/f9/LegendECUExternalROM.pdf

I need some more time to map out all the digital circuits. But I am hoping we can come up with an elegant solution where we put a single 512Kb ROM on a small daughter board that would sit on top of the existing ROM socket and with a few reversible modification to the ECU board, make the MCU run the entire engine program externally. With that, work can then begin on modifying the core engine assembly program to support things such as custom MAP sensors, PWM solenoids, etc.

One last thing; I noticed you put the MCU into mode 3. That enables memory segment paging; I am not sure if it has any effects on the program but I would think mode 1 would be more appropriate since it keep the memory address space the same as mode 2. But mode 3 is definitely useful later if we need to expand the program beyond the 64K memory space.

Thanks!

Eddy

). I honestly don't even know where to start with modifying the code to support boost, I know the main thing is to hold the ECU in open loop once boost is being produced. There are other things I'd like to find such as coil pack dwell time, etc.